FPGA UARTを実装する(1)

- atliqu

- 2020年8月19日

Basys3を実用的に使用するためには、ボード上に搭載されている出力デバイスでは不足でPCに繋ぐ必要があります。 Basys3にはUART-USBブリッジが搭載されていますので、それを使ってみます。

Vivadoで使用できるIPを探してみたのですが、AXIバスで使用するUARTは用意されていますが、一般的なUARTはありません。 ネット上で検索すると、色々ソースが公開されていますので、それらを参考にしながら作成することにしました。

Lチカや7セグの点灯程度の規模では直接コーディングできたのですが、今回は多少複雑なので、事前検討しながら進めていきます。

ネット上のソースをコピペすれば機能は実現できるのですが、実験が目的なので、結果的にコードが同じになったとしても内容を理解したいです。

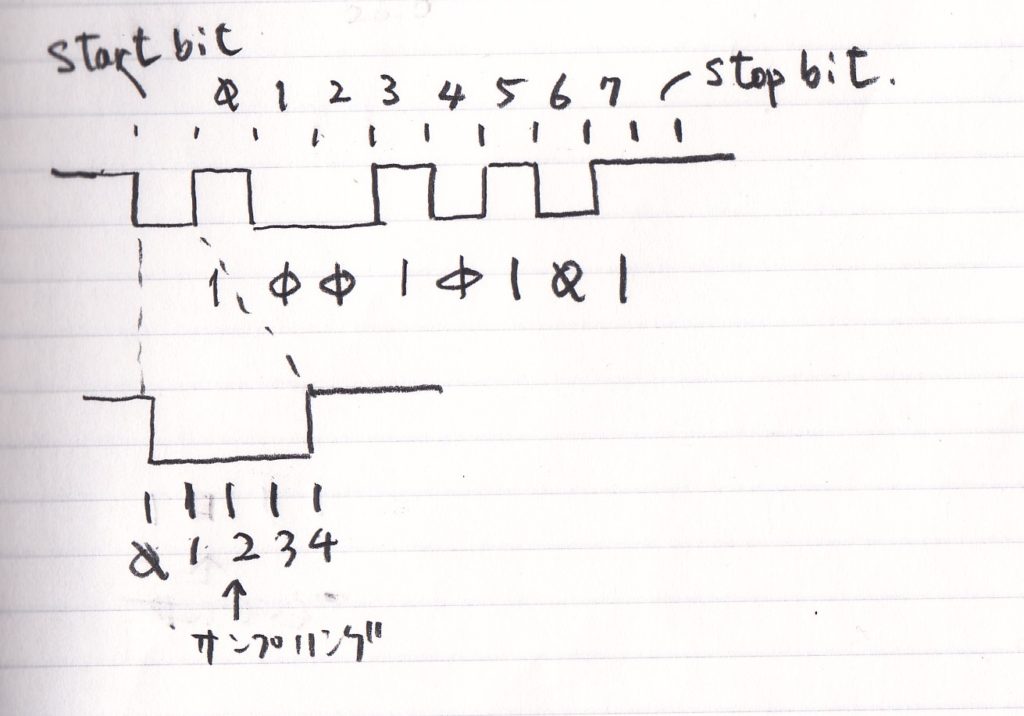

まず、受信の方から検討します。 RXDから流れ込んでくるデータは、下記のようになります。

スタートビットを検出して、それぞれのビットの中央付近でサンプリングしてやればよさそうですが、FPGAのクロックに対して、RXDデータは非同期で入ってくるので、ずれることを考慮する必要があります。

上図のように、1ビットを4分割して2の位置でサンプリングすることを基準にしてやれば、ずれても1または3の位置でサンプリングできそうです。

したがって、RXDのビット周期の4分の1の周期で入力信号をチェックして、スタートビットを検出し、その後、2の位置での信号をシフトレジスタに入れていくということを10ビット分繰り返せばよさそうです。