SDRの作成(1)

- atliqu

- 2020年9月26日

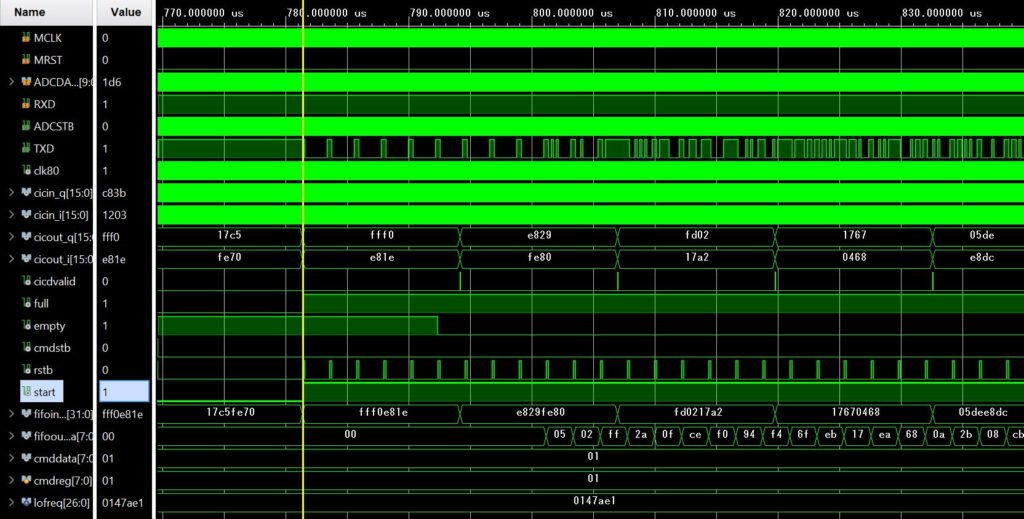

いままでブロック毎に動作をシミュレーションしてきましたが、FIFOを追加して全体をまとめました。 FIFOの深さは、最終的には512にする予定ですが、今回は、64にしています。 512だとFIFOがフルになるのに6.55ms必要で、シミュレーションに時間がかかるためです。 64だと819μsで済みます。

ソースです。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 |

module SDR_2020( input MCLK, input MRST, input signed [9:0] ADCDATA, input RXD, output ADCSTB, output TXD ); wire clk80; wire signed [15:0] cicin_q, cicin_i, cicout_q, cicout_i; wire cicdvalid, full, empty, cmdstb, rstb, start; wire [31:0] fifoindata; wire [7:0] fifooutdata, cmddata; reg [7:0] cmdreg = 8'b00000000; parameter lofreq = 27'h147ae1; //800kHz CLK80 CLK80(.clk_out1(clk80), .clk_in1(MCLK)); Complex_Mixer Complex_Mixer(.mixCLK(clk80), .mixRST(MRST), .mixSIG(ADCDATA), .mixFREQ(lofreq), .mixOUT_Q(cicin_q), .mixOUT_I(cicin_i)); cicfilter cicfilter(.cicCLK(clk80), .cicRST(MRST), .DATAIN_Q(cicin_q), .DATAIN_I(cicin_i), .DATAOUT_Q(cicout_q), .DATAOUT_I(cicout_i), .cicDATAVALID(cicdvalid)); asfifo asfifo(.wr_clk(~cicdvalid), .rd_clk(rstb), .din(fifoindata), .wr_en(1), .rd_en(1), .dout(fifooutdata), .full(), .almost_full(full), .empty(empty)); //32bitx512 UART_RX UART_RX(.rxRST(MRST), .rxCLK(clk80), .rxRXD(RXD), .rxDATAREADY(cmdstb), .rxDATA(cmddata)); UART_TX UART_TX(.txDATA(fifooutdata), .txRST(MRST), .txCLK(clk80), .txSTART(start), .txLOAD(rstb), .txTXD(TXD)); assign ADCSTB = ~clk80; assign fifoindata = {cicout_q, cicout_i}; assign start = full && (cmdreg == 8'b00000001); always @(posedge clk80) begin if(MRST) cmdreg <= 8'b00000000; else if(cmdstb) cmdreg <= cmddata; end endmodule |

ほとんどは、すでにシミュレーションで確認されたモジュールを組み合わせているだけなので、簡単な構成です。 データは、垂れ流しでもいいと思いますが、一応コマンドを受け取ってから吐き出すようにしています。

ローカルオシレータの発振周波数は、800kHz固定です。

テストベンチです。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 |

module SDR2020_sim; reg clk, rst = 0, rxd_ = 1; wire adcstb_, txd_; wire signed [9:0] adcdata_; reg [9:0] add = 0; reg signed [9:0] mem[0:1023]; parameter STEP = 10, bitperiod = 200; //baudrate 5000000 reg [9:0] rightshift; reg [7:0] cmddata = 8'b00000001; integer i; always begin clk <= 0; #(STEP/2); clk <= 1; #(STEP/2); end always @(posedge adcstb_ or posedge rst) begin if(rst) add <= 0; else add <= add + 1; end; assign adcdata_ = mem[add]; SDR_2020 SDR_2020(.MCLK(clk), .MRST(rst), .ADCDATA(adcdata_), .ADCSTB(adcstb_), .TXD(txd_), .RXD(rxd_)); initial begin $readmemb("simrom.txt", mem); rst = 1; #(STEP*35); rst = 0; #STEP rightshift <= {1'b1, cmddata, 1'b0}; for(i = 0; i < 10; i = i + 1) begin #STEP; rxd_ <= rightshift[0]; #STEP; rightshift <= rightshift >> 1; #bitperiod; end #(STEP*1200); $finish; end endmodule |

シミュレーション結果です。

FIFOがフルになる少し前にstart信号が発生して、TXDからデータが出始めているのが確認できました。

一応、FPGAの開発は一段落したので、これからはPC側のソフトの開発を行います。