Basys3

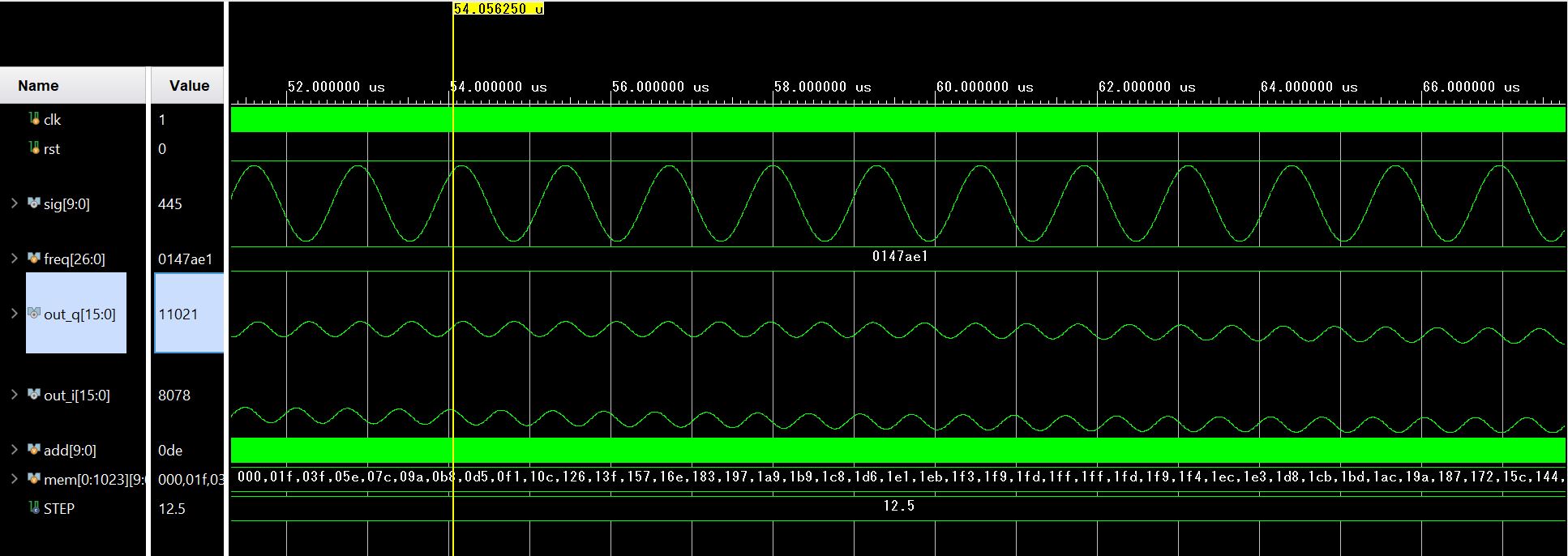

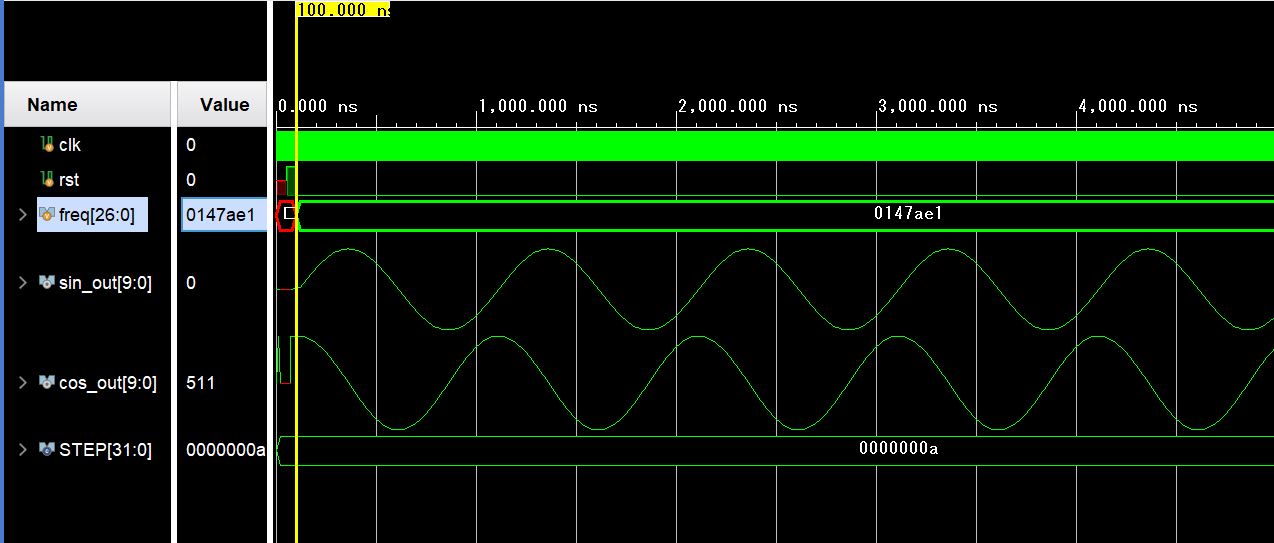

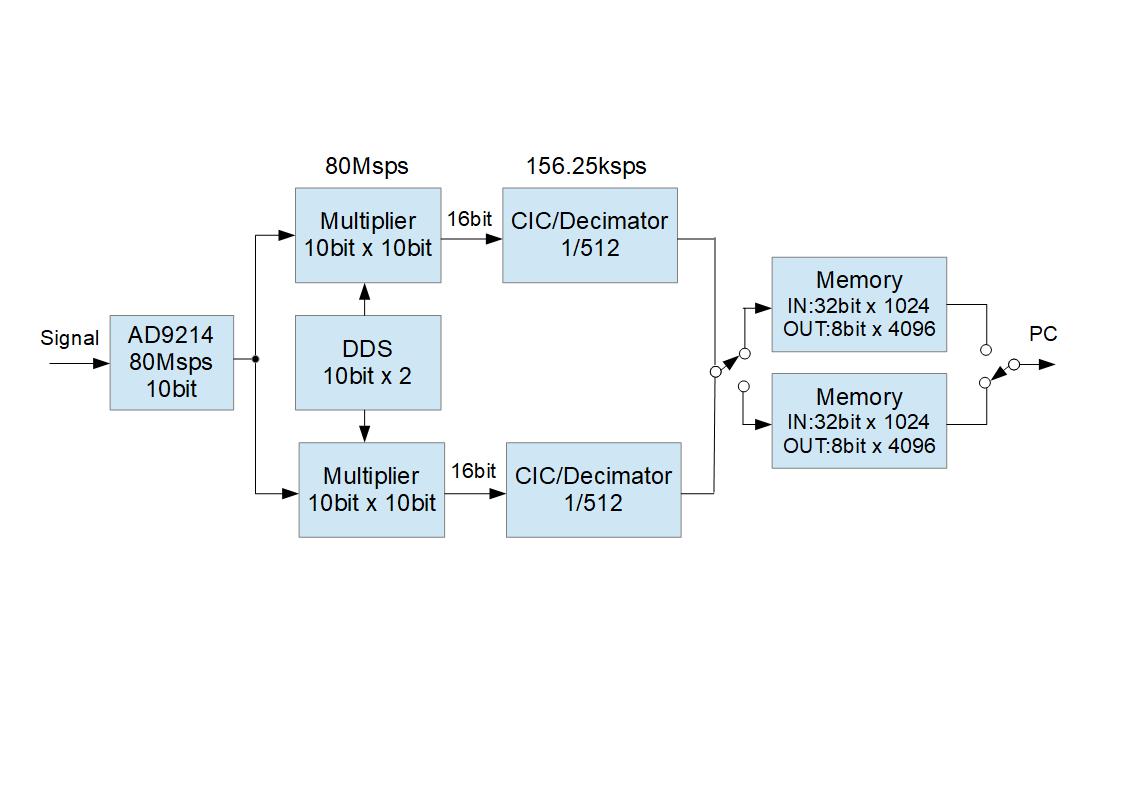

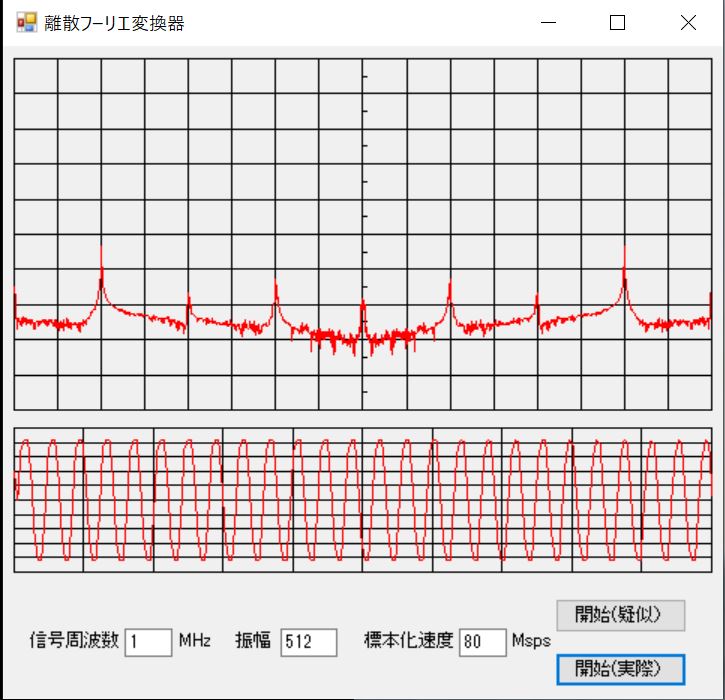

簡易スペクトラムアナライザ(3)

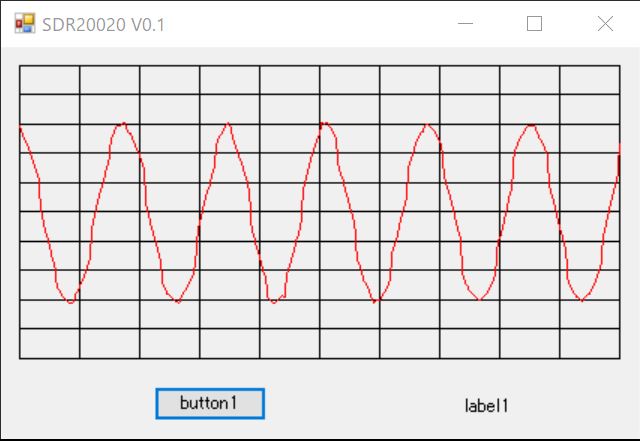

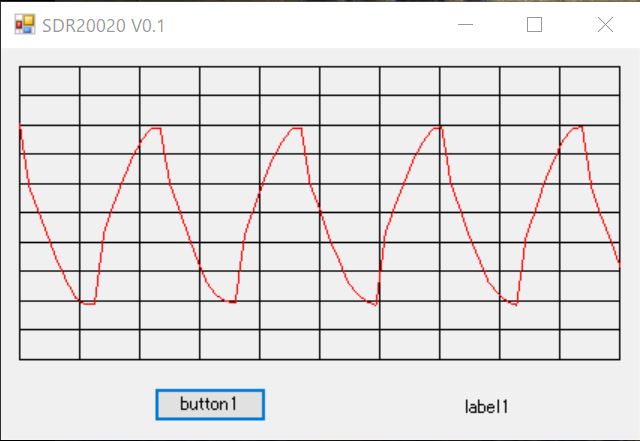

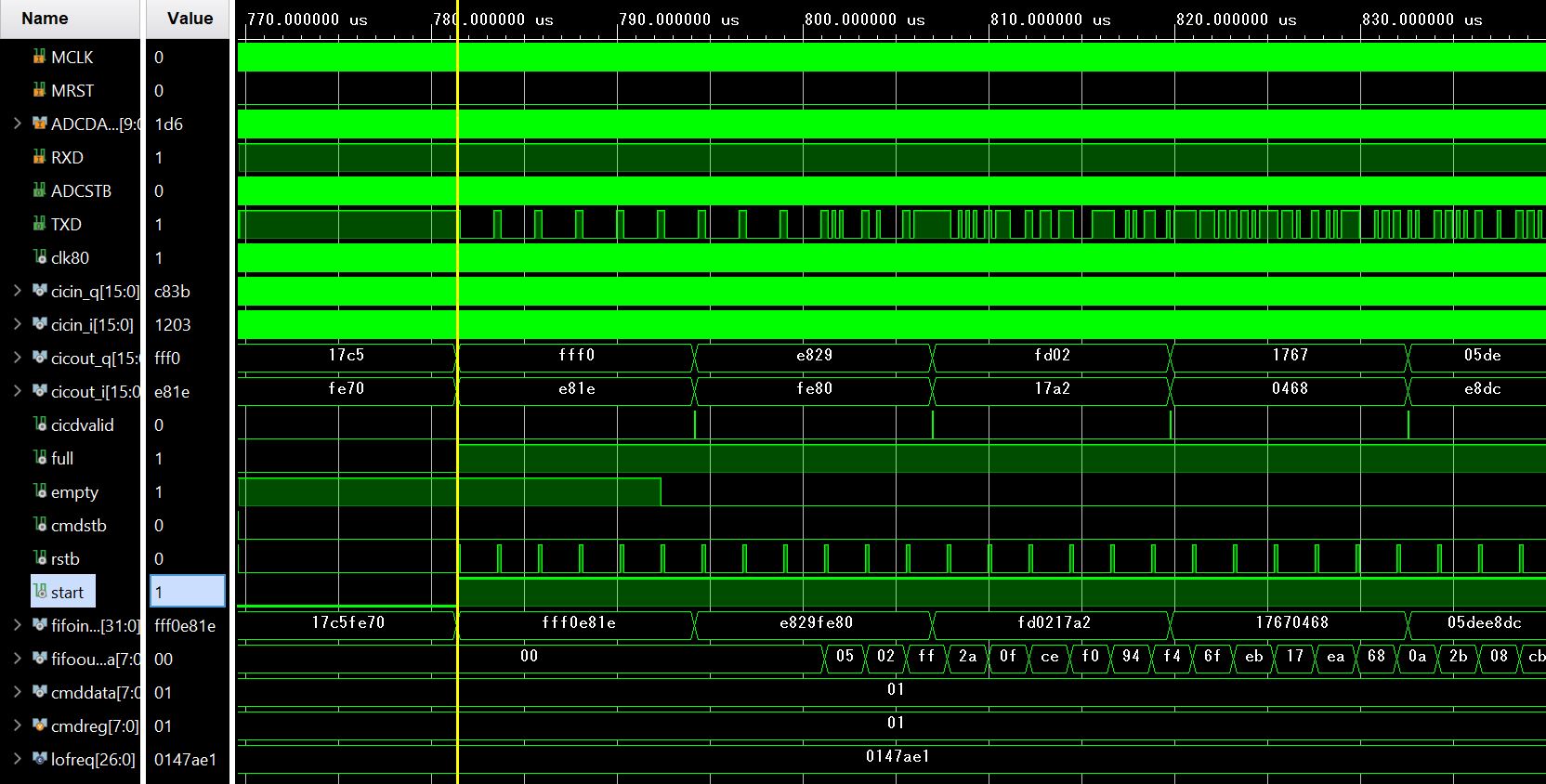

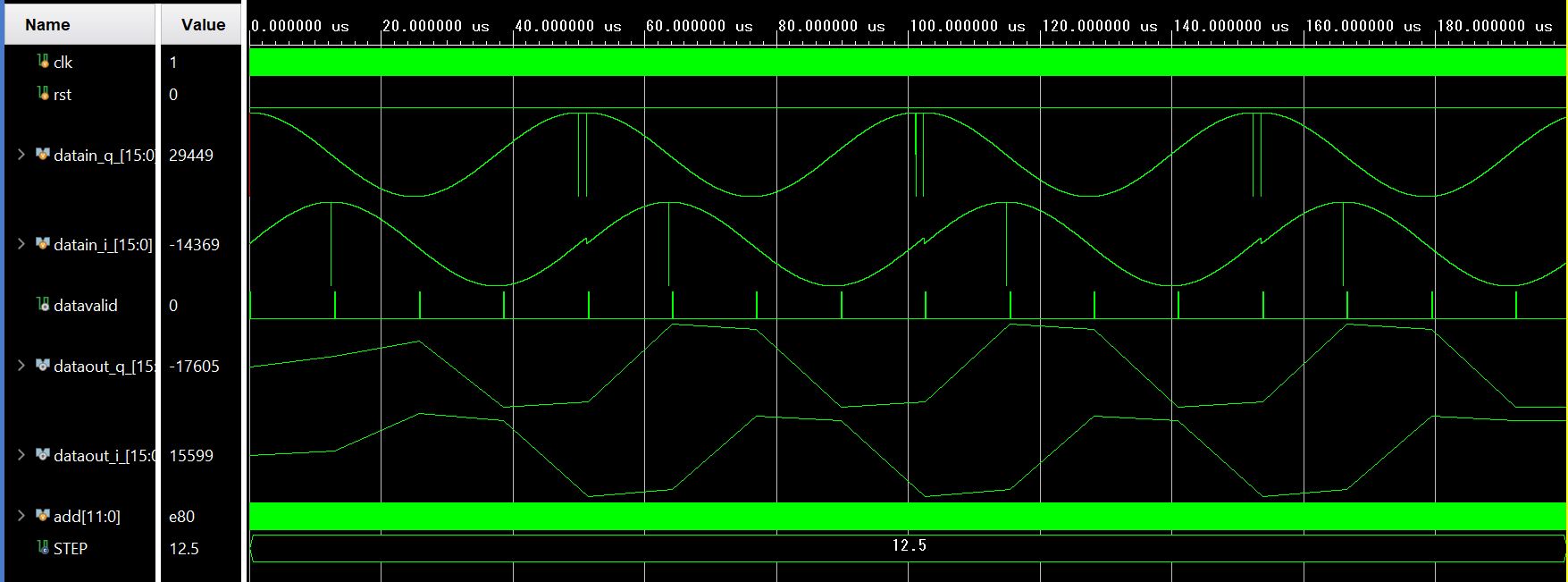

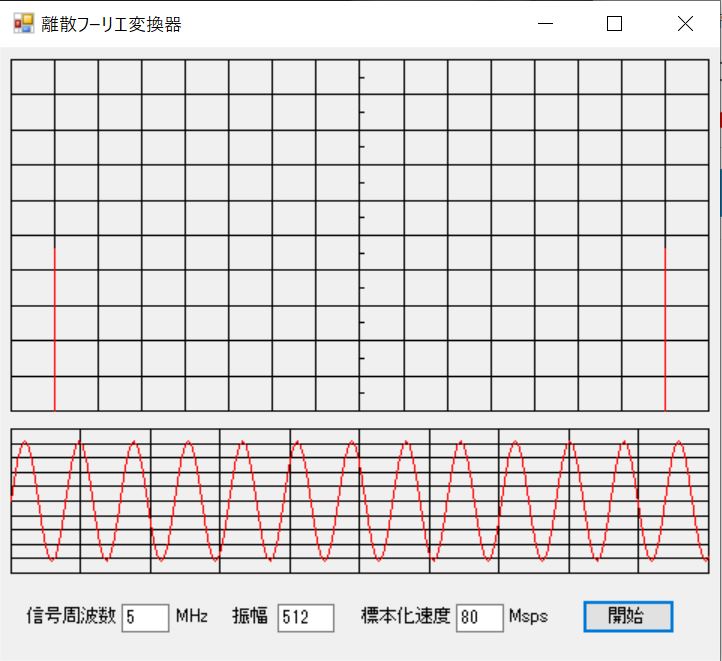

ADCでキャプチャした信号をDFTしてみました。 10MHzの信号を入力しました。 ダミーと違って入力波形がそれなりに歪んでいるので、10MHz以上の成分も検出されています。 0~40MHzまでしか測 ...

続きを読む簡易スペクトラムアナライザ(2)

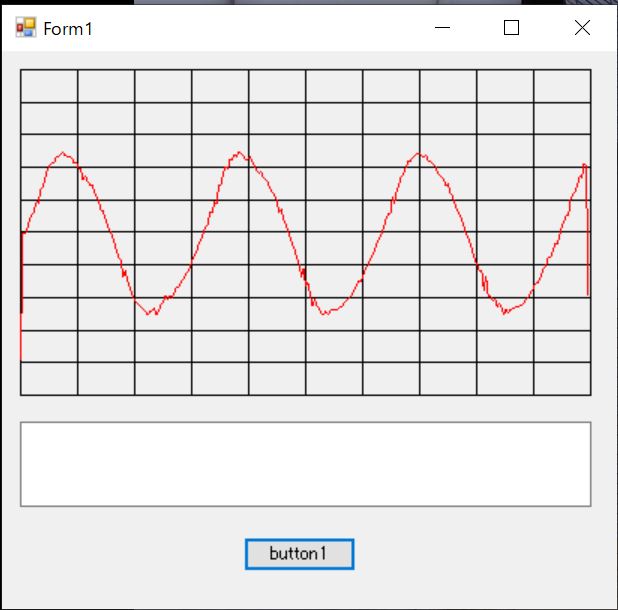

前回は、ブログに数式を記入するだけで力尽き、本文まで書けなかったので、今回はその続きです。 実際にC#でプログラムしてみました。 普通は、フーリエ変換というとFFTだと思うのですが、データ数が少なく、 ...

続きを読む

最近のコメント