FPGA UART TX

- atliqu

- 2020年8月21日

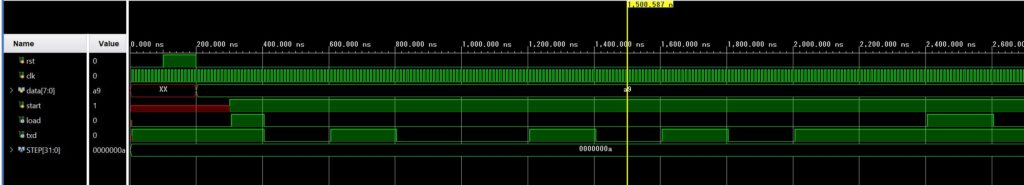

今回は、UARTの送信側。 txDATAに送信データを書き込んで、txSTARTで送信を開始し、10bit送信したらtxLOADで次のデータをtxDATAに書き込む。

ソースです。

module UART_TX(

input txRST,

input txCLK,

input [7:0] txDATA,

input txSTART,

output reg txLOAD,

output reg txTXD

);

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 |

reg [15:0] cnt; reg [3:0] bitcnt; reg [9:0] shiftreg; reg shift; reg clr_bitcnt; reg stat, nexstat; always @(posedge txCLK) begin if(txRST) begin stat <= 1'b0; cnt <= 16'h0; bitcnt <= 4'h0; end else begin cnt <= cnt + 16'h1; if(cnt >= 19) begin //baud rate 5M stat <= nexstat; cnt <= 16'h0; if(txLOAD) shiftreg <= {1'b1, txDATA, 1'b0}; if(clr_bitcnt) bitcnt <= 4'h0; if(shift) begin shiftreg <= shiftreg >> 1; bitcnt <= bitcnt + 4'h1; end end end end always @(posedge txCLK) begin txLOAD <= 1'b0; shift <= 1'b0; clr_bitcnt <= 1'b0; txTXD <= 1'b1; case(stat) 0: begin if(txSTART) begin nexstat <= 1'b1; txLOAD <= 1'b1; shift <= 1'b0; clr_bitcnt <= 1'b0; end else begin nexstat <= 1'b0; txTXD <= 1'b1; end end 1: begin if(bitcnt >= 9) begin nexstat <= 1'b0; clr_bitcnt <= 4'h1; end else begin nexstat <= 1'b1; txTXD <= shiftreg[0]; shift <= 1'b1; end end default: nexstat <= 1'b0; endcase end |

endmodule

テストベンチです。

module sim_UART_TX;

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 |

localparam STEP = 10; reg rst; reg clk; reg [7:0] data; reg start; wire load; wire txd; UART_TX UART_TX( .txRST (rst), .txCLK (clk), .txDATA (data), .txSTART (start), .txLOAD (load), .txTXD (txd) ); always begin clk = 0; #(STEP/2); clk = 1; #(STEP/2); end initial begin rst = 0; #(STEP*10); rst = 1; #(STEP*10); rst = 0; data <= 8'ha9; #(STEP*10); start <= 1; #(STEP*250); $stop; end |

endmodule