ADCで信号をキャプチャする(4)

- atliqu

- 2020年9月9日

テストベンチです。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 |

module ADC2020_sim; reg clk, rst = 0, txd = 1; wire signed [9:0] adcsim; reg [7:0] add = 0; wire stb, rxd; reg signed [9:0] mem[0:255]; parameter STEP = 10; //10nS integer i; reg [9:0] rightshift; parameter bit_period = 200; //5Mbaud=200nS reg [7:0] cmddata = 1; assign adcsim = mem[add]; always begin clk = 0; #(STEP/2); clk = 1; #(STEP/2); end always @(posedge stb) add <= add + 1; ADC2020 ADC2020(.MCLK(clk), .MRST(rst), .STB(stb), .ADC_DATA(adcsim), .RXD(txd), .TXD(rxd)); task comwrite; input [7:0] cmddata; begin #STEP rightshift <= {1'b1, cmddata, 1'b0}; for(i=0; i < 10; i = i + 1) begin #STEP txd <= rightshift[0]; #STEP rightshift <= rightshift >> 1; #bit_period; end end endtask initial begin $readmemb("simdata.txt", mem); #(STEP*50) rst = 1; txd = 1; #STEP rst = 0; comwrite(cmddata); #(STEP*200000); $finish; end endmodule |

あらかじめ”simdat.txt”にADCのデータを作成しておきます。 最初に$readmembで、simdat.txtのデータを読み込んでstbでメモリのアドレスをカウントして、adcsimにADCのデータを渡します。

task comwriteで、コマンドを1ビットづつ5Mボーで送り、後はデータが送られてくるのを待ちます。

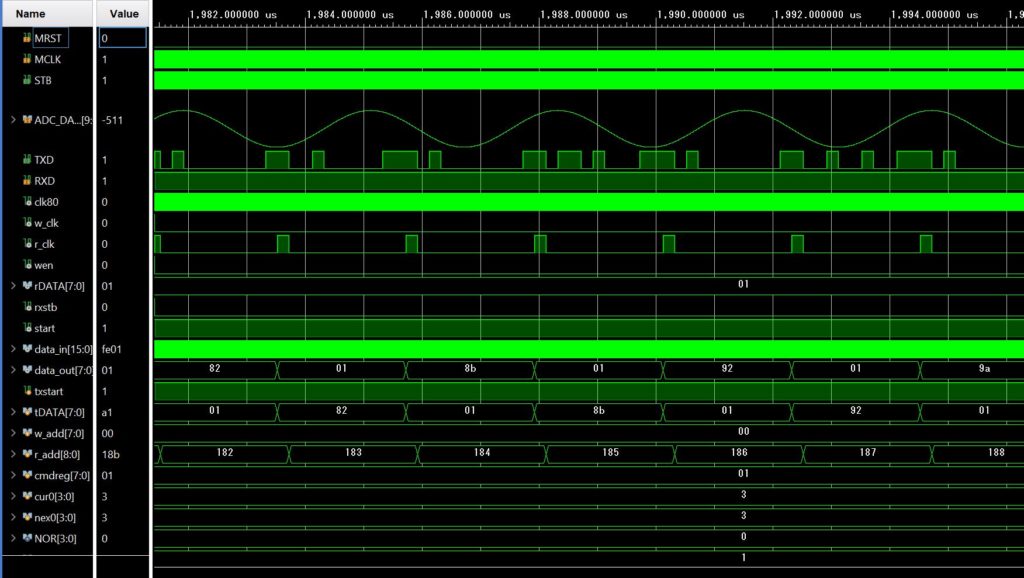

シミュレーション結果です。

ADCデータは、アナログ表示にしています。 TXDからデータが送信されているのが確認できました。