SDRの検討(1)

- atliqu

- 2020年9月17日

ADCでキャプチャした信号を複素ミキサーで低周波領域に変換して、PCに取り込んでフィルタリング、復調し、サウンドドライバで音を出すという、所謂ダイレクトサンプリング方式のSoftware Defined Radioを作りたいと思います。

PCでのソフトを含めかなり大がかりなプロジェクトになるので、いつ完成するかわかりませんし、途中でやーめた..ということもあり得るのですが、やれるところまでやってみましょう。

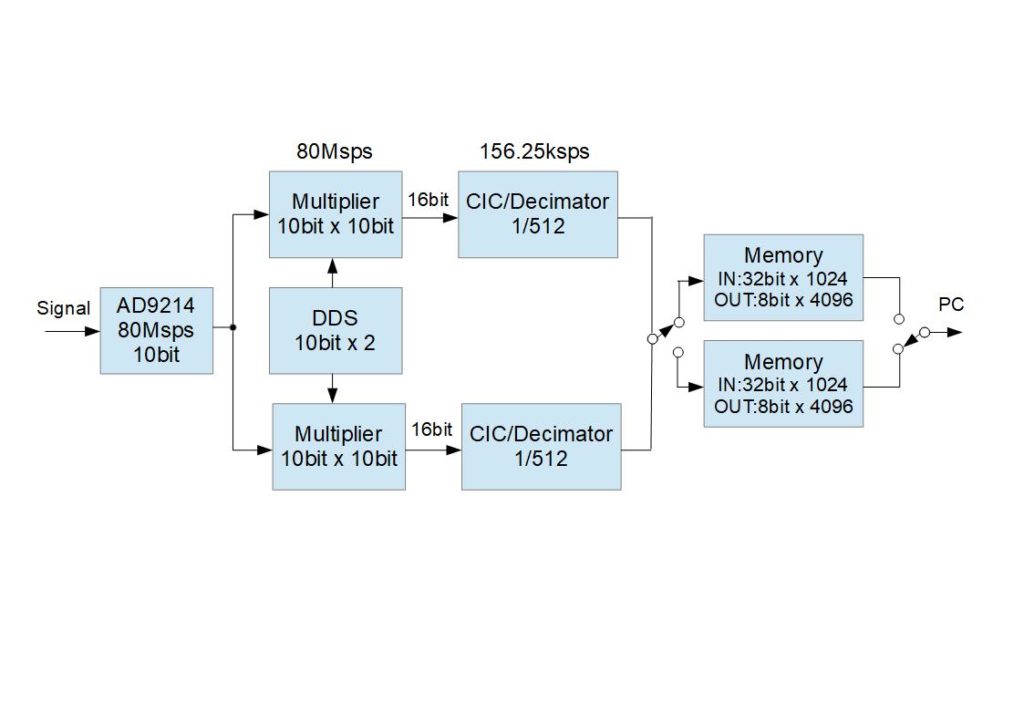

とりあえず、FPGAでの構成を考えました。

入力信号を10bit 80Mspsでサンプリングします。 これは、例のADCで行います。 この先は、Basys3の中の処理です。

DDSで10bitのsin波とcos波を生成します。 10bitの入力信号と10bitのDDS信号を乗算して20bitの低周波出力を得ます。 20bitの低周波出力の上位16bitをCICフィルタでデシメーションします。 デシメーション率は、1/512とします。 デシメーション率は、処理能力との関係で大きくする必要があるかもしれません。 デシメーションすることにより、サンプリング速度は、156.25kspsになります。16bitのI信号とQ信号で32bitの信号を生成し、メモリに格納します。 ADCからの信号は、切れ目なく連続して発生するので、メモリを2つ用意して、PCが読み出している間に他のメモリにADCデータを書き込むということを繰り返して処理します。 なので、書き込む時間よりPCが読み出す時間が短いことが必要です。 また、メモリは入出力が非対称のメモリで、入力32bit、出力8bitとします。

UARTの速度は、現在5Mbpsとしているので、スタートビットとストップビットを入れると500kBpsになります。 データは、32bitで156.25kspsなのでByte当たりの速度は、625kBpsとなり間に合いません。

UARTの速度を上げるか、デシメーション率を上げる必要があります。 これは、実験してみて決めたいと思います。